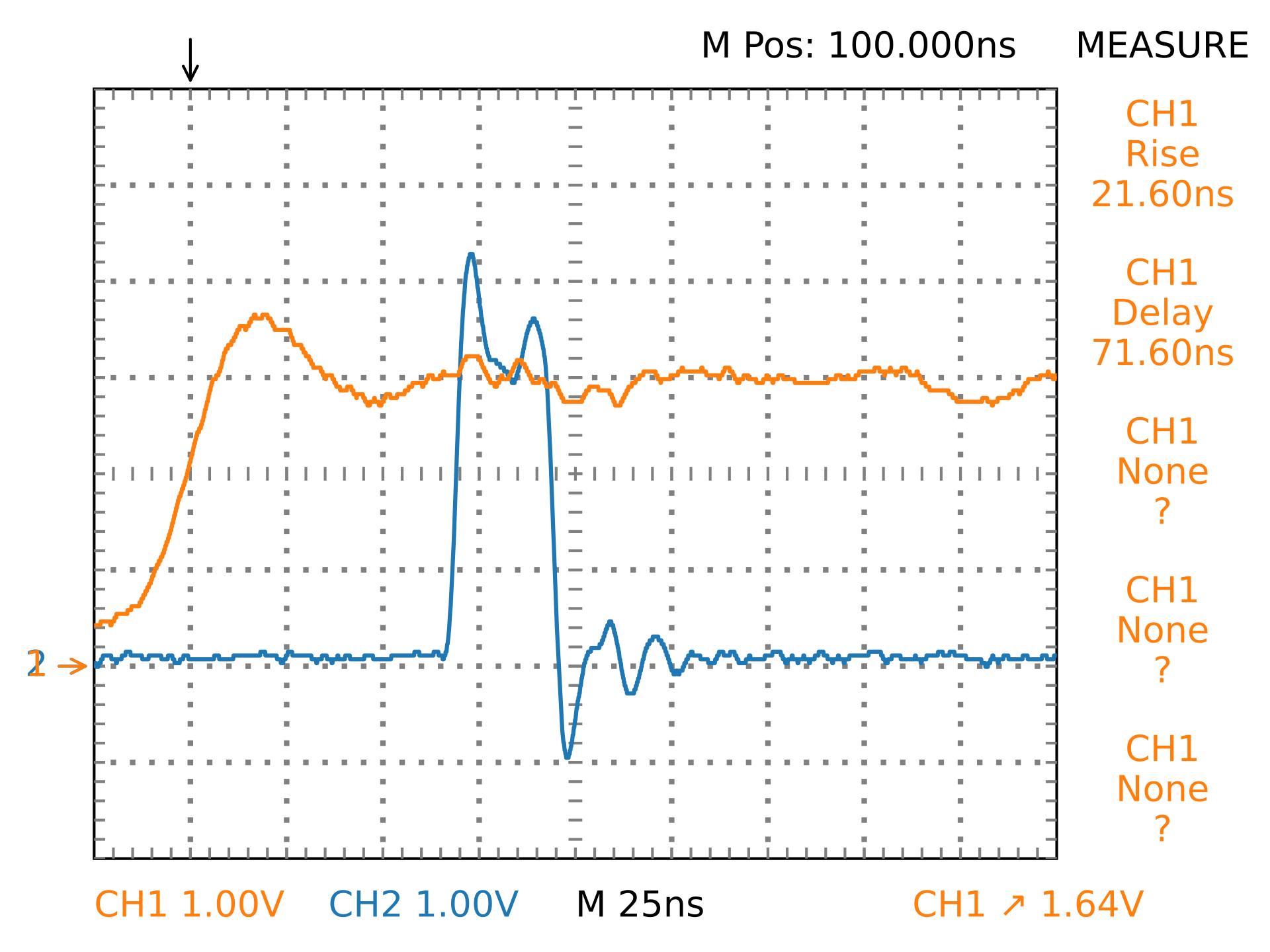

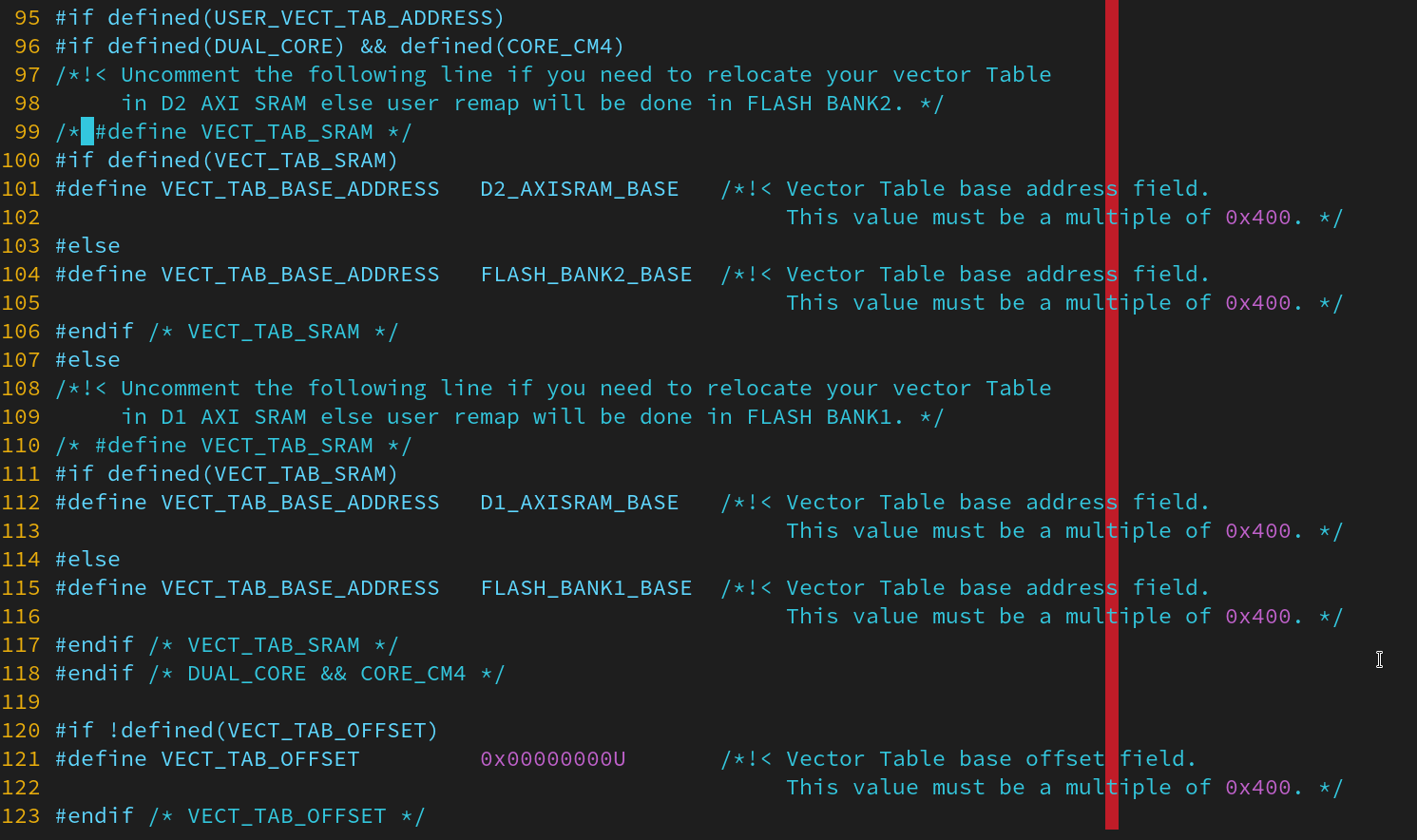

Keep optimizing IRQ latency on the STM32H743 @ 480 MHz. The 70 ns vs. 100 ns overhead mystery solved. I did not correctly relocate the vector table to Tightly-Coupled Memory properly, it was still in Flash. The STM32 HAL macro USER_VECT_TAB_ADDRESS is a flag, not a memory address! In fact, only several hardcoded addresses are available, a real user override is not provided (the name "user" is a lie). Solution: just change VTOR manually, don't trust the startup code. I'm now getting 70-ns IRQ without CPU cache. #electronics #STM32

If you have a fediverse account, you can quote this note from your own instance. Search https://mk.absturztau.be/notes/ajvb448y305b01i4 on your instance and quote it. (Note that quoting is not supported in Mastodon.)

![void relocate_to_itcm(void)

{

extern volatile char _si_isr_vector;

extern volatile char __isr_vector_start, __isr_vector_end;

volatile char *flash_isr_vector_start = &_si_isr_vector;

volatile char *ram_isr_vector_start = &__isr_vector_start;

volatile char *ram_isr_vector_end = &__isr_vector_end;

size_t len = ram_isr_vector_end - ram_isr_vector_start;

for (size_t i = 0; i < len; i++) {

ram_isr_vector_start[i] = flash_isr_vector_start[i];

}

#ifdef SEMIHOSTING

printf("relocate %p-%p to %p, %d bytes\n", flash_isr_vector_start, flash_isr_vector_start + len, ram_isr_vector_start, len);

#endif

extern volatile char _si_itcm_text;

extern volatile char __itcm_text_start, __itcm_text_end;

volatile char *flash_itcm_text_start = &_si_itcm_text;

volatile char *ram_itcm_text_start = &__itcm_text_start;

volatile char *ram_itcm_text_end = &__itcm_text_end;

len = ram_itcm_text_end - ram_itcm_text_start;

for (size_t i = 0; i < len; i++) {

ram_itcm_text_start[i] = flash_itcm_text_start[i];

}

#ifdef SEMIHOSTING

printf("relocate %p-%p to %p, %d bytes\n", flash_itcm_text_start, flash_itcm_text_start + len, ram_itcm_text_start, len);

#endif

SCB->VTOR = D1_ITCMRAM_BASE;

}](https://misskey-taube.s3.eu-central-1.wasabisys.com/files/c723bcd1-5045-4a11-87b9-9ed3383c3af5.png)